# Design and implementation of a digital FIR notch filter for the ECG signals using FPGA

Dr. Kamal Aboutabikh<sup>1</sup>, Dr. Ibrahim Haidar<sup>2</sup>, Dr. Nader Aboukerdah<sup>3</sup>

Faculty of Engineering, Kassala University, Kassala, Sudan<sup>1</sup>

Faculty of Engineering, Alwatania University, Hamma, Syria<sup>2</sup>

Faculty of Engineering, Aleppo University, Aleppo, Syria<sup>3</sup>

**Abstract:** This paper introduce a practical elimination of PLI (power line interference) with the frequency of 50 Hz and its 2<sup>nd</sup>, 3<sup>rd</sup> and 4<sup>th</sup> harmonics using digital FIR notch filter designed by FPGA chips Which is situated on development and education board DE2-70. To realize the filtering operation a digital multiband stop filter has been designed for frequencies 50Hz, 100Hz, 150Hz, and 200Hz with high order 1500 and processing word of 10bits and frequency 1000Hz to gain attenuation of 60dB for PLI signal components. Using FPGA to design digital FIR notch filter enable as of realization parallel processing to achieve digital convolution algorithm in the real time, where 1500 operation of adding, shifting, multiplying and dividing can be done in 0.5 ms (sampling period) for digital samples of 10 bits length, this equivalent 3 million operation per second where the general processor cannot do that.

Key words: FPGA, DDFS, ECG, notch filer.

# I. INTRODUCTION

-All ECG, EEG and EMG devices use filter for PLI (power) signal (50 Hz) to eliminate its influence on accuracy and reliability of the data taken from these devices.

-Most of ECG, EEG and EMG devices use digital FIR filter notching filter to eliminate PLI signal (50 Hz) only this will cause its harmonics to penetrate directly or by induction to ECG signal and this will influence the measurement results and readings and errors in the state of the patient.

-In Ref [1], Seema Verma presents a digital Notch filter design using Hamming window to remove the effect of power line interference (PLI) with frequency of 50 Hz and attenuation of 13.4 dB is obtained. Also, presents an adaptive filter design to remove the effect of PLI and attenuation of 34.2 dB is obtained.

-In Ref [2], Rupali Madhukar Narsale, Dhanashri Gawali and Amit Kulkarni presents a digital notch filter design with frequency of 50 Hz and with band width of 45 to 55 Hz by using FPGA with sampling frequency of 500 Hz, and attenuation of 13 dB.

-In Ref [3], Manoj Sharma, Hemant dalal present a digital FIR filter with order of 450 and different windows to remove the effect of PLI and attenuation of 18 dB are obtained.

-In Ref [4], Mbachu C.B presents a method of designing digital notch filter with Kaiser window and order of 100 and with interference signals attenuation of 13 dB.

In Ref [5] ,Mbachu C.B and Offor K.Jpresents a digital FIR filter for reducing 50Hz power line noise in ECG signal is designed and implemented with Hamming window.

In this paper we try to introduce a new idea not only to eliminate PLI signal but also its harmonics which considered with negative effect not less than the first

-All ECG, EEG and EMG devices use filter for PLI harmonic on the measurement results of ECG, EEG and (power) signal (50 Hz) to eliminate its influence on EMG devices and the like of medical devices.

Another idea of using one multi band stop digital filter to eliminate the PLI signal and its harmonics. That will make the filter economic and high effective and that will increase the accuracy and reliability of the devises.

# II. THE IMPORTANT OF THE RESEARCH AND ITS PURPOSES

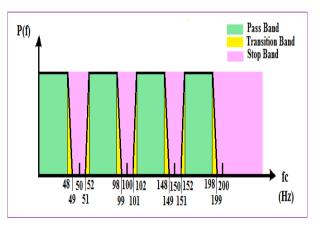

-Elimination of PLI signal and its harmonicsup to 4<sup>th</sup>by direct and induction methods with the following bands: (48... 52 Hz) , (98...102 Hz), (148...152 Hz) and

(198...102 Hz), (198...102 Hz), (148...152 Hz) and (198...102 Hz) according to Fig.1 through designing one digital FIR notching filter of multi band stop without using several filters keeping the phase response linear.

-Using the proposed filter we get high accuracy and reliability of the measurement results for ECG, EEG and EMG devices.

Fig.1 The pass and stop bands of digital FIR notching filter.

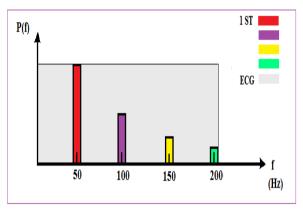

-Testing the designed filter through simulated ECG signal using direct digital frequency synthesizer (DDFS\_ECG) and simulated interference sine signal (DDFS\_PLI) with 4 harmonics (50, 100, 150 and 200 Hz) according to Fig.2 using digital oscilloscope (GDS-1052U).

Fig.2 The spectrum of PLI signal and its harmonics

# III. THE USED TOOLS AND SOFTWARE

In this research, the following tools and software are used: -Digital programmable device (Cyclone II EP2C70F896C6 FPGA, Altera), which was placed on an education and development board (DE2-70, Terasic) [6].

-DDFS which is considered as highly accuracy technique in frequency synthesizing domain and they were designed on digital programmable device.

-Digital FIR filters of highly accuracy specifications in filtering, stability and linear phase response.

-VHDL programming language with Quartus II 9.1 design environment.

-MATLAB11 programming environment for digital filter designing and filter coefficients computing.

-GDS-1052U digital oscilloscope with Free Wave program to take the results.

-PC computer for designing and injecting the design in the chip.

## VI. BLOCK DIAGRAM OF THE IMPLEMENTED DESIGN

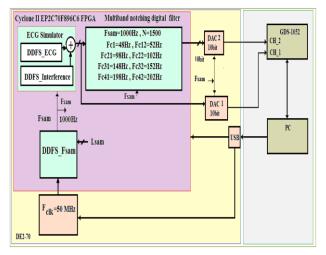

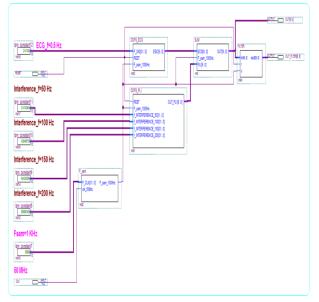

A block diagram of the design is shown in Fig.3 and Fig.4 shows the design diagram in the programming environment QUARTUS II 9.1 implemented on digital IC from ALTERA company type: Cyclone II EP2C70F896C6 FPGA situated on DE2-70 which is composed of the following blocks:

-Direct digital frequency synthesizer DDFS\_ECG to form ECG signal which is very close the real signal.

-Direct digital frequency synthesizer DDFS\_PLI to form the interference signal which has the harmonics: 50, 100,150 and 200 Hz simultaneously.

-Multi bands digital FIR filter with the bands mentioned by the convolution algorithm in time domain  $(F_{c11},F_{c12})$ ,  $(F_{c21},F_{c22})$ ,  $(F_{c31},F_{c32})$  and  $(F_{c41},F_{c42})$ .

-Two DAC of 10bits to convert the signal from digital to analog form, before filtering (DAC1) and after filtering (DAC2).

-PC computer to link DE2-70 board via USB and inject the design in the Cyclone II EP2C70F896C6 FPGA chip [6].

-Digital oscilloscope GDS-1052U connected to PC via USB to show the input and output signals of the multiband digital filters in time and frequency domains due to various interference signals ,where (ON CH\_1:Before Filtering ,ON CH2 After Filtering).

Fig.3 Block diagram of study and research procedures for ECG signal.

Fig.4 The design diagram in the environment Quartus II 9.1

This design implemented for ECG signal and digital FIR notching filter mentioned before.

## V. SPECIFICATIONS OF ECG SIGNAL

-Frequency range of ECG signal: (0...200 Hz). -The processing on ECG signal frequency:  $F_{signal} = 1 \text{ Hz}$ equal to 60 BPM. -Sampling frequency:  $T_{sam} = 1 \text{ ms}$ ;  $F_{sam} = 1000 \text{ Hz}$ .

-Number of samples: M=1501.

Signed 10 bit. -Cut off -SNRinp ratio: SNRinp = 1/1 for the component 50 Hz,  $F_{c12}=52$ Hz SNRinp = 2/1 for the component 100Hz, -Cut off f

SNRinp = 4/1 for the component 150Hz, and SNRinp =  $F_{c22}=102Hz$ 8/1 for the component 200Hz. -Cut off fr

## VI. DIGITAL FIR NOTCHING FILTER SPECIFICATIONS

-Length of the filter coefficients word: signed 10bit.

-Number of used digital multiplier: 1501 multiplier 10x10 bit.

-Number of parallel shift registers with 10 bit length. 1500SR.

-One adder with 1501 input and one output 30bit.

-Mathematical and logic operations elements (AND, NOT, XOR...)

-Filter cut off frequencies:

$$F_{c11} = 48 \ Hz$$

,  $F_{c12} = 52 \ Hz$ ,  $F_{c21} = 98 \ Hz$ ,  $F_{c22} = 102 \ Hz$

$F_{c11} = 148 \ Hz$ ,  $F_{c12} = 152 \ Hz$ ,  $F_{c21} = 198 \ Hz$ ,  $F_{c22} = 202 \ Hz$

$$r_{c31} = 140 \ H_{c} \ , r_{c32} = 152 \ H_{c} \ , r_{c41} = 150 \ H_{c} \ , r_{c42} = 202$$

-Sampling frequency:  $F_{sam} = 1000$  Hz.

-Filter order: N=M-1=1500.

-Attenuation factor: -60 dB stop band attenuation.

-The possibility of developing the algorithm through coupling several filters serially.

#### **VII. FILTERING ALGORITHM**

The output signal of FIR filter can be simulated according to the following mathematical convolution relation [7]:

$$y(n) = h(n) * x(n) = \sum_{m=0}^{M-1} h(m) \cdot x(n-m)$$

(1)

Where:

-x(n) :samples of input signals in digital form.

-M: numbers of samples for impulse response.

-m: number of the sample for filter impulse response.-N: number of the sample for input and output signal.-h(n) :samples of FIR digital filter and can be given for BSF according to the following mathematical relation [7]:

$$h(0) = 1 - 2\left(\frac{F_{c2i} - F_{c1i}}{F_{sam}}\right), \quad For \ n = 0$$

$$h(n) = \frac{1}{\pi n} \left[\sin\left(2\pi n \frac{F_{c1i}}{F_{sam}}\right) - \sin\left(2\pi n \frac{F_{c2i}}{F_{sam}}\right)\right], \text{ For } n \neq 0 \quad (2)$$

Where:

$$-\left(\frac{M-1}{2}\right) \le n \le +\left(\frac{M-1}{2}\right) \tag{3}$$

-i band stop number of BSF i=(1...4).

$-F_{c1i}$ : 1<sup>st</sup> cut off frequency for the BSF cut band i,  $F_{c1i}$ : 2nd cut off frequency for the BSF cut band i,  $F_{sam}$  sampling frequency of input signal.

-The coefficients of the digital multi band BSF filter can be calculated from MATLABII according to the following specifications:

-Length of processing word for ECG discrete signal:  $-F_{sam} = 1000$  Hz.

-Cut off frequencies for the first band:  $F_{c11}\!\!=\!\!48Hz,\ F_{c12}\!\!=\!\!52Hz$

-Cut off frequencies for the second band:  $F_{c21}{=}98Hz, \ F_{c22}{=}102Hz$

-Cut off frequencies for the third band:  $F_{c31}{=}148 Hz, \ F_{c32}{=}152 Hz$

-Cut off frequencies for the fourth band: Fc41=198Hz,  $F_{c42}{=}202\text{Hz}$

-Order of the filter: N=1500.

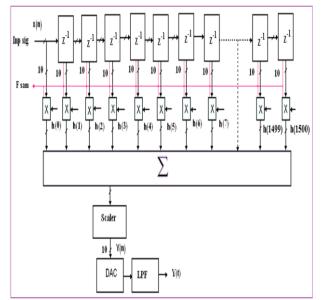

Fig.5 shows the convolution algorithm for FIR filter and input sample signal and impulse response signals with long M.

Where Z a delay line with long 10bit and delay equual to sample pulse period  $T_{sam}$ .

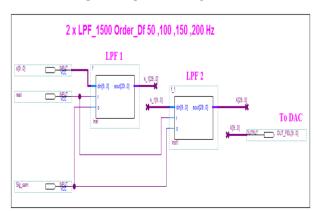

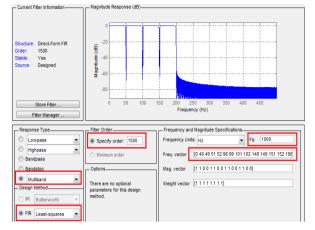

This filter has been designed using VHDL [8] inside QuartusII 9.1 and it is composed of two serial BSF filters as shown in Fig.6, Fig.7 shows the specifications of the filter in MATLABII according to the specifications mentioned before.

Fig.5 Time convolution  $\{y(n)\}$  for samples of input signal and impulse response of length M=1501.

Fig.6 Block diagram of the digital BSF filter.

IJARCCE

Fig.7 Specification of the notch filter in MATLABII with frequency band 200 Hz.

## VII. PRACTICAL RESULTS

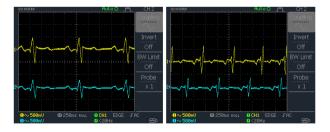

-The results of the practical design for different cases of interference signals in time and frequency domain for ECG signal before and after filtering can be taken by the digital oscilloscope GDS- 1052U.

-Fig.8 shows on channel 1of the oscilloscope ECG signal with the components QRS which formed by DDFS\_ECG with the special specifications mentioned before without the effect of PLI interference signal before filtering, while channel 2 shows ECG signal after filtering by the multi bands FIR notching filter, this ensure that the filter must not distort the signal after filtering because the phase linearity response of the filter.

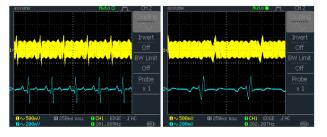

-Fig.9 shows on channel 1of the oscilloscope ECG signal with the effect of PLI signal with frequencies (50,100,150 and 200 Hz) in –band with SNRinp = 1/1,2/1,4/1 and 8/1befor filtering , while channel 2 shows ECG signal after filtering by the multi bands FIR notching filter in time domain.

Fig. 8 Input and output signal for the digital filter without noise.

Fig.9 Input and output signal for the digital filter with PLI interference signal and its harmonics in time domain.

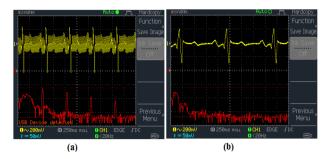

-Fig.10-a shows ECG signal before filtering and Fig.10-b shows ECG signal after filtering in frequency domain where we can see that interference signal has been attenuated by 60 dB.

#### **IX. RESULTS AND FUTURE WORK**

-The practical results show that the designed multi band digital filter eliminate PLI signal and its 4 harmonics successfully by using one filter for SNRinp = 1/1 keeping amplitude and phase for ECG signal specifications with attenuation factor of 60 dB, and the specifications can be improved by increasing the order of the filter or couple more than one filter serially this cab realized using FPGA.

-In this paper DDFS\_ECG and DDFS\_PLI with its harmonics and the digital filter has been designed successfully and the implemented practical results ensure the possibility of using this type of filters in ECG, EGG and EMG devices.

-This algorithm can be applied in all ECG, EGG and EMG devices.

-For developing the research in the future a real ECG signal from any patient person and use the proposed filter.

#### REFERENCES

- SeemaVerma . "Reduction Of Noise From ECG Signal Using FIR Low Pass Filter With Various Window Techniques" published in Engineering, Science and Technology (CREST) Journals, Vol 01, Issue 05, July 2013, 117-122.

- [2] RupaliMadhukarNarsale, DhanashriGawali and AmitKulkarni. FPGA Based Design & Implementation of Low Power FIR Filter for ECG Signal Processing/ International Journal of Science, Engineering and Technology Research (IJSETR), Volume 3, Issue 6, June 2014 1673.

- [3] Manoj Sharma, Hemantdalal. Designing and Implementation of Digital Filter for Power line Interference Suppression/International Journal of Science, Engineering and Technology Research (IJSETR), Volume 3, Issue 6, June 2014.

- [4] Mbachu C.B et al. Processing ECG Signal with Kaiser Window based FIR digital filters / International Journal of Engineering Science and Technology (IJEST), Vol. 3 No. 8 August 2011.

- [5] Mbachu C.B and Offor K.J. Reduction of powerline noise in ECG signal using FIR digital filter implemented with Hamming window / International Journal of Science, Environment and Technology, Vol. 2, No 6, 2013, 1380 – 1387.

- [6] -www.altera.com.

- [7] Steve Winder .2002-Analog and Digital Filter Design, second edition, Elsevier Science (USA), 450.

- [8] Volnei A. Pedroni. 2004-Circuit Design with VHDL. MIT Press Cambridge, Massachusetts London, England, 364.

# BIOGRAPHIES

**Dr. Kamal Aboutabikh** holds a PhD in communication engineering in 1988 from the USSR, university of communication in Leningrad, holds a degree assistant professor in 2009 from Aleppo University. Lecturer at

Department of Biomedical Engineering, Al Andalus University For Medical Sciences-Syria, Tishreen University-Syria, Corduba Private University- Syria and Kassala University-Sudan. Publish a lot of research in the field of digital communication and digital signal processing in the universities of Syria and in the European and Indian journals. Working in the field of programming FPGA by using VHDL and design of Digital Filters.

**Dr. Ibrahim Haidar** holds a PhD in communication engineering in 1985 from the Aston University in England, holds a degree professor in 2006 from Aleppo University. Lecturer at Corduba Private University- Syria. Publish a lot of research in the field of digital

communication in the universities of Syria. Working in the field of digital communication systems and programming FPGA by using VHDL and design of Digital Filters.

**Dr. Nader Aboukerdah** holds a PhD in communication engineering in 2001 from the Egypt University of Communication in Cairo, holds a degree assistant professor in 2012 from Aleppo University. Lecturer at Department of Biomedical

Engineering, Al Andalus University for Medical Sciences, Syria. Publish a lot of research in the field of digital communication in the universities of Syria. Working in the field of programming FPGA by using VHDL and design of Digital Filters.